# Si8281/82/83/84 数据表

### 带集成直流转换器的 ISODrivers

Si828x(Si8281/82/83/84)产品系列由拥有集成系统安全和反馈功能的高电流隔离栅极 驱动器组成。这些设备非常适合用于驱动 MOSFET 和 IGBT,可广泛用于各种逆变器和电 机控制应用。Si828x 隔离栅极驱动器采用 Silicon Labs 自主研发的硅隔离技术,支持 符合 UL1577、高达 5.0 kVrms 的耐受电压。与其他隔离栅极驱动器技术相比,通过此技 术可获得更高性能,减少温度和寿命差异,零件匹配更紧密,并提供优异的共模抑制比。

除栅极驱动器外,Si828x 产品系列还集成了一个直流控制器,可轻松控制驱动器端的隔 离电源。基于可用的系统电压轨和所需用电量,Si828x 直流控制器提供两种不同的配置 供您订购。Si8281 和 Si8283 产品系列使用集成电源开关,但仅限符合设备偏压的直流-直流电压输入。Si8282 和 Si8284 产品系列采用外接电源开关,能允许更高的电压输入 电源轨。用户可调节频率有助于减少放热,软启动功能更安全,并提供多种关闭选项可供 选择。该设备仅需极小的无源元件和微型变压器。

设备输入为互补数字输入,适用于多种设置。隔离输入端还拥有多个控制和反馈数字信 号。设备控制器可接收设备驱动器端功耗状态和故障状态的相关信息,并通过低电平有效 复位引脚将设备从故障状态中恢复。

Si828x 设备输出端拥有单独的上拉和下拉栅极引脚。专用的 DSAT 引脚可检测去饱和条件,并能以可控方式快速关闭驱动器。Si828x 设备还集成了米勒钳位功能,有助于有效 关闭电源开关。

### 应用

- IGBT/MOSFET 门驱动器

- 工业、混合动力汽车(HEV)以及可再生能源逆变器

- 交流、无刷以及直流电机控制和驱动

- 变速电机控制器

- 隔离的开关模式电源和 UPS 电源

### 安全法规认证(正在申请)

- UL 1577 认证

- 1 分钟内最大 5000 V<sub>RMS</sub>

- CSA component notice 5A 认证

- IEC 60950-1、61010-1、60601-1(强化绝缘)

- VDE 认证合规

- IEC 60747-5-5/VDE0884 第 10 部分

- CQC 认证

- GB4943.1

#### 主要特点

- 系统安全功能

- 去饱和(DESAT)检测

- 故障反馈

- 欠压锁定(UVL0)

- 故障状态软关闭

- Silicon Labs 的高性能隔离技术

- 业界领先的抗噪声干扰能力

- 高速、低延时及低偏移

- 提供最佳可靠性

- 30 V 驱动器端供电电压

- 集成米勒钳位功能

- 电源就绪引脚

- 互补驱动器控制输入

- 紧凑封装: 20 引脚和 24 引脚宽体 SOIC

- 集成直流转换器

- 低电磁干扰(EMI)的反馈控制转换器

- 83% 的直流转换器效率

- 关机、频率和软启动控制

- 工业温度范围: -40 至 125 °C

# 1. Ordering Guide

| Ordering Part             | UVLO    |          | DC/DC Features |                      |                 |            |  |  |

|---------------------------|---------|----------|----------------|----------------------|-----------------|------------|--|--|

| Number (OPN)              | Voltage | Shutdown | Soft Start     | Frequency<br>Control | External Switch | -          |  |  |

| Si8281BD-IS               | 9 V     | No       | No             | No                   | No              | WB SOIC-20 |  |  |

| Si8281CD-IS               | 12 V    | No       | No             | No                   | No              | WB SOIC-20 |  |  |

| Si8282BD-IS               | 9 V     | No       | No             | No                   | Yes             | WB SOIC-20 |  |  |

| Si8282CD-IS               | 12 V    | No       | No             | No                   | Yes             | WB SOIC-20 |  |  |

| Si8283BD-IS<br>(Sampling) | 9 V     | Yes      | Yes            | Yes                  | No              | WB SOIC-24 |  |  |

| Si8283CD-IS<br>(Sampling) | 12 V    | Yes      | Yes            | Yes                  | No              | WB SOIC-24 |  |  |

| Si8284BD-IS<br>(Sampling) | 9 V     | Yes      | Yes            | Yes                  | Yes             | WB SOIC-24 |  |  |

| Si8284CD-IS<br>(Sampling) | 12 V    | Yes      | Yes            | Yes                  | Yes             | WB SOIC-24 |  |  |

### 2. System Overview

### 2.1 Isolation Channel Description

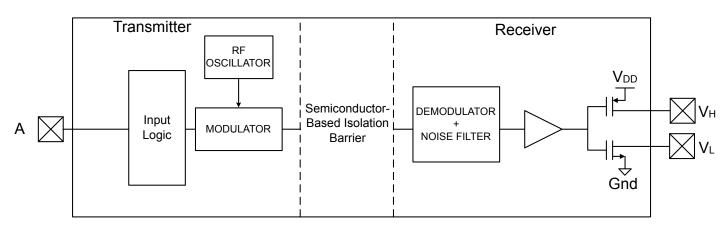

The operation of an Si828x channel is analogous to that of an optocoupler and gate driver, except an RF carrier is modulated instead of light. This simple architecture provides a robust isolated data path and requires no special considerations or initialization at start-up. A simplified block diagram for a single Si828x channel is shown in the figure below.

Figure 2.1. Simplified Channel Diagram

A channel consists of an RF Transmitter and RF Receiver separated by a semiconductor-based isolation barrier. Referring to the Transmitter, input A modulates the carrier provided by an RF oscillator using on/off keying. The Receiver contains a demodulator that decodes the input state according to its RF energy content and applies the result to output B via the output driver. This RF on/off keying scheme is superior to pulse code schemes as it provides best-in-class noise immunity, low power consumption, and better immunity to magnetic fields.

### 2.2 Device Behavior

The following table shows state relationships for the Si828x inputs and outputs.

| Table 2.1. Si8281/82/83/84 Truth Tab | ole |

|--------------------------------------|-----|

|--------------------------------------|-----|

| IN+   | IN– | VDDA State | VDDB–VMID<br>State | Desaturation<br>State | VH      | VL                     | RDY | FLTb |

|-------|-----|------------|--------------------|-----------------------|---------|------------------------|-----|------|

| Н     | н   | Powered    | Powered            | Undetected            | Hi-Z    | Pull-down              | Н   | Н    |

| н     | L   | Powered    | Powered            | Undetected            | Pull-up | Hi-Z                   | Н   | Н    |

| L     | х   | Powered    | Powered            | Undetected            | Hi-Z    | Pull-down              | Н   | Н    |

| Х     | Х   | Powered    | Unpowered          | _                     | _       | —                      | L   | Н    |

| Х     | х   | Powered    | Powered            | Detected              | Hi-Z    | Pull-down <sup>1</sup> | Н   | L    |

| Note: |     |            |                    | 1                     |         |                        |     |      |

1. Driver state after soft shutdown.

### 2.3 Input

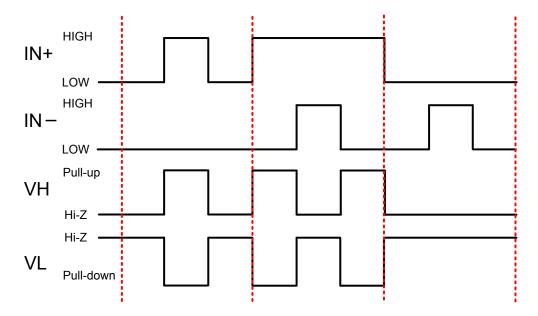

The IN+ and IN– inputs to the Si828x devices act as a complementary pair. If the IN– is held low, the IN+ will act as a active-high input for the driver control. Alternatively, if IN+ is held high, then the IN– can be used as an active-low input for driver control. When the IN– is used as the control signal, taking the IN+ low will hold the output driver low.

Figure 2.2. Si828x Complementary Input Diagram

### 2.4 Driver Side Output

The Si828x has separate pins for gate drive high (VH) and gate drive low (VL). This makes it simple for the user to use different gate resistors to control IGBT  $V_{CF}$  rise and fall time.

### 2.5 Fault (FLTb) Pin

FLTb is an open-drain type output. Once the UVLO condition is cleared on the driver side of the device, the FLTb pin is released. A pull-up resistor takes the pin high. When the desaturation condition is detected, the Si828x indicates the fault by bringing the FLTb pin low. FLTb stays low until the controller brings the RSTb pin low.

FLTb is also taken low if the UVLO condition is met during device operation. FLTb is released in that case as soon as the UVLO condition is cleared.

### 2.6 Reset (RSTb) Pin

The RSTb pin is used to clear the desaturation condition and bring the Si828x driver back to an operational state. Even though the input may be toggling, the driver will not change state until the fault condition has been reset.

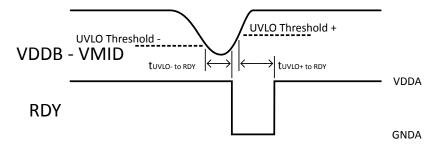

### 2.7 Ready (RDY) Pin

The ready pin indicates to the controller that power is available on both sides of the isolation, i.e., at VDDA and VDDB. RDY goes high when both the primary side and secondary side UVLO circuits are disengaged. If the UVLO conditions are met on either side of the isolation barrier, the ready pin will return low. RDY is a push-pull output pin and can be floated if not used.

### 2.8 Undervoltage Lockout (UVLO)

The UVLO circuit unconditionally drives VL low when VDDB is below the lockout threshold. The Si828x is maintained in UVLO until VDDB rises above VDDB<sub>UV+</sub>. During power down, the Si828x enters UVLO when VDDB falls below the UVLO threshold plus hysteresis (i.e., VDDB  $\leq$  VDDB<sub>UV+</sub> – VDDB<sub>HYS</sub>).

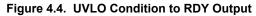

#### 2.9 Desaturation Detection

The Si828x provides sufficient voltage and current to drive and keep the IGBT in saturation during on time to minimize power dissipation and maintain high efficiency operation. However, abnormal load conditions can force the IGBT out of saturation and cause permanent damage to the IGBT.

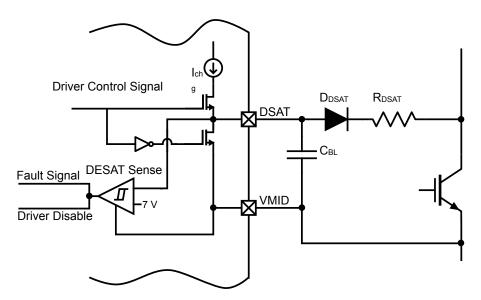

To protect the IGBT during abnormal load conditions, the Si828x detects an IGBT desaturation condition, shuts down the driver upon detecting a fault, and provides a fault indication to the controller. These integrated features provide desaturation protection with minimum external BOM cost. The figure below illustrates the Si828x desaturation circuit. When the Si828x driver output is high, the internal current source is on, and this current flows from the DSAT pin to charge the C<sub>BL</sub> capacitor. The voltage on the DSAT pin is monitored by an internal comparator. Since the DSAT pin is connected to the IGBT collector through the D<sub>DSAT</sub> and a small R<sub>DSAT</sub>, its voltage is almost the same as the V<sub>CE</sub> of the IGBT. If the V<sub>CE</sub> of the IGBT does not drop below the Si828x desaturation threshold voltage within a certain time after turning on the IGBT (blanking period) the block will generate a fault signal. The Si828x desaturation hysteresis is fixed at 220 mV and threshold is nominally 7 V.

Figure 2.3. Desaturation Circuit

As an additional feature, the block supports a blanking timer function to mask the turn-on transient of the external switching device and avoid unexpected fault signal generation. This function requires an external blanking capacitor,  $C_{BL}$ , of typically 390 pF between DSAT and VMID pins. The block includes a 1 mA current source ( $I_{Chg}$ ) to charge the  $C_{BL}$ . This current source, the value of the external  $C_{BL}$ , and the programmed fault threshold, determine the blanking time ( $t_{Blanking}$ ).

$$t_{Blanking} = C_{BL} \times \frac{V_{DESAT}}{I_{chg}}$$

An internal nmos switch is implemented between DSAT and VMID to discharge the external blanking capacitor, C<sub>BL</sub>, and reset the blanking timer. The current limiting R<sub>DSAT</sub> resistor protects the DSAT pin from large current flow toward the IGBT collector during the IGBT's body diode freewheeling period (with possible large collector's negative voltage, relative to IGBT's emitter).

### 2.10 Soft Shutdown

To avoid excessive dV/dt on the IGBT's collector during fault shut down, the Si828x implements a soft shut down feature to discharge the IGBT's gate slowly. When soft shut down is activated, the high power driver goes inactive, and a weak pull down via VH and external RH discharges the gate until the gate voltage level is reduced to the VSSB + 2 V level. The high power driver is then turned on to clamp the IGBT gate voltage to VMID.

After the soft shut down, the Si828x driver output voltage is clamped low to keep the IGBT in the off state.

### 2.11 Miller Clamp

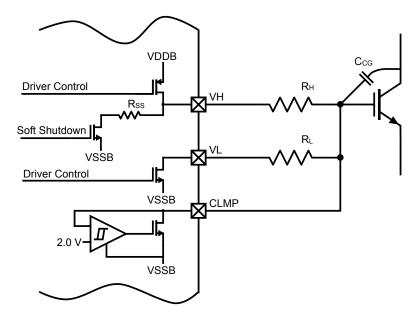

IGBT power circuits are commonly connected in a half bridge configuration with the collector of the bottom IGBT tied to the emitter of the top IGBT.

When the upper IGBT turns on (while the bottom IGBT is in the off state), the voltage on the collector of the bottom IGBT flies up several hundred volts quickly (fast dV/dt). This fast dV/dt induces a current across the IGBT collector-to-gate capacitor ( $C_{CG}$  that constitutes a positive gate voltage spike and can turn on the bottom IGBT. This behavior is called Miller parasitic turn on and can be destructive to the switch since it causes shoot through current from the rail right across the two IGBTs to ground. The Si828x Miller clamp's purpose is to clamp the gate of the IGBT device being driven by the Si828x to prevent IGBT turn on due to the collector  $C_{CG}$  coupling.

Figure 2.4. Miller Clamp Device

The Miller clamp device (Clamp) is engaged after the main driver had been on (VL) and pulled IGBT gate voltage close to VSSB, such that one can consider the IGBT being already off. This timing prevents the Miller clamp from interfering with the driver's operation. The engaging of the Miller Clamp is done by comparing the IGBT gate voltage with a 2.0 V reference (relative to VSSB) before turning on the Miller clamp NMOS.

#### 2.12 DC-DC Converter Application Information

The Si828x isolated dc-dc converter is based on a modified fly-back topology and uses an external transformer and rectifying diodes for low cost and high operating efficiency. The PWM controller operates in closed-loop, current mode control and generates isolated output voltages with up to 2 W average output power at VDDP = 5.0 V. Voltage feedback is referenced between VDDB-VSSB. Although there is only one voltage feedback path, two output voltages are realized by the tight coupling of the two secondary transformer windings. Options are available for 24 Vdc input operation and externally configured switching frequency.

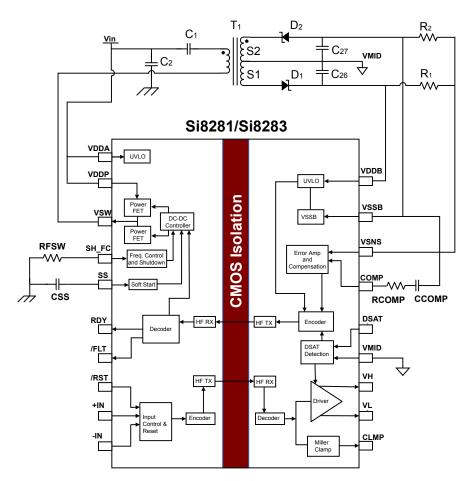

The dc-dc controller modulates a pair of internal, primary-side power switches (see Figure 2.5 Si8281/83 Block Diagram: 3 V–5 V Input to Split Voltage Output on page 8) to generate an isolated voltage at external diode D1 and D2. Divider resistors, R1 and R2, generate proper 1.05 V for the VSNS pin. Closed-loop feedback is provided by an internal compensated error amplifier, which compares the voltage at the VSNS pin to an internal voltage reference. The resulting error voltage is fed back across the isolation barrier via an internal feedback path to the controller, thus completing the control loop.

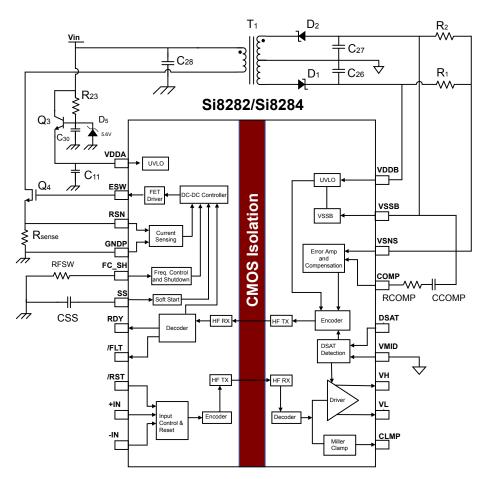

For input supply voltages higher than 5 V, an external FET Q2 is modulated by a driver pin ESW as shown in Figure 2.6 Si8282/84 Block Diagram: >5.5 V Input to Split Voltage Output on page 9. A shunt resistor based voltage sense pin, RSN, provides current sensing capability to the controller.

The Vin must be able to support the Si828x VDDB-VSSD static load current (approximately 9 mA), the output drive load requirement, and the dc-dc power dissipation (loss). The driver power requirement is dependent on the IGBT gate charge and the driver switching frequency. Below are the equations to calculate the Vin power requirement.

$$Pvin = \frac{\left(9 \times 10^{-3} \times (VDDB + VSSB) + Qg \times Fsw\right)}{n}$$

where:

Qg = IGBT total gate charge

Fsw = driver switching frequency

$\eta$  = dc-dc efficiency (approximately 78%)

Additional part number features include an externally-triggered shutdown of the converter functionality using the SH pin and a programmable soft start configured by a capacitor connected to the SS pin. The resistor value on pin SH/FC and the capacitor value on pin SS are used during power-up to set the dc-dc switching frequency. Note that pin SH/FC and SS pins are available on the Si8283 and Si8284 only. The Si828x can be used with a low-voltage power rail or a high-voltage power rail. These features and configurations are explained in more detail in other sections.

### 2.12.1 External Transformer Driver

The dc-dc controller has internal switches (VSW) for driving the transformer with up to a 5.5 V voltage supply. For higher voltages on the primary side, a driver output (ESW) is provided on the Si8282 and Si8284 that can switch an external NMOS power transistor for driving the transformer. When this configuration is used, a shunt resistor based voltage sense pin (RSN) provides current sensing to the controller.

### 2.12.2 Output Voltage Control

The isolated output voltage, VOUT (VDDB–VSSB), is sensed by a resistor divider that provides feedback to the controller through the VSNS pin. The voltage error is encoded and transmitted back to the primary side controller across the isolation barrier, which in turn changes the duty cycle of the transformer driver. The equation for VOUT is as follows:

$$VOUT = VSNS \times \left(1 + \frac{R1}{R2}\right)$$

The VDDB-VSSB voltage split is depended on the ratio of the two secondary windings and can be calculated as follows:

$$VDDB - VMID = VOUT \times \left(\frac{S1}{S1 \times S2}\right)$$

$$VSSB - VMID = VOUT \times \left(\frac{S2}{S1 + S2}\right)$$

### 2.12.3 Compensation

The dc-dc converter operates in current mode control. The loop is compensated by connecting an external resistor in series with a capacitor from the COMP pin to VSSB. The compensation network, RCOMP, and CCOMP are set to 200 k $\Omega$  and 1 nF for most Si828x applications.

#### 2.12.4 Thermal Protection

A thermal shutdown circuit is implemented to protect the system from over-temperature events. The thermal shutdown is activated at a junction temperature that prevents permanent damage from occurring.

#### 2.12.5 Cycle Skipping

Cycle skipping is included to reduce switching power losses at light loads. This feature is transparent to the user and is activated automatically at light loads. The product options with integrated power switches (Si8281/83) may never experience cycle skipping during operation, even at light loads, while the external power switch options (Si8282/84) are likely to have cycle skipping start at light loads.

#### 2.12.6 Shutdown (Si8283 and Si8284 Only)

This feature allows the operation of the dc-dc converter to be shut down when SH/FC is asserted high. This pin normally has a resistor to ground, the value of which is used in conjunction with the value of the capacitor on the SS pin during startup to determine the dc-dc switching frequency. Therefore, a GPIO pin connected to SH/FC pin to control the shutdown function should be in a high-impedance state during startup to avoid interfering with the internal frequency calculation circuit. During normal operation, this pin should be held low and only taken high to assert dc-dc shutdown.

#### 2.12.7 Soft Start (Si8283 and Si8284 Only)

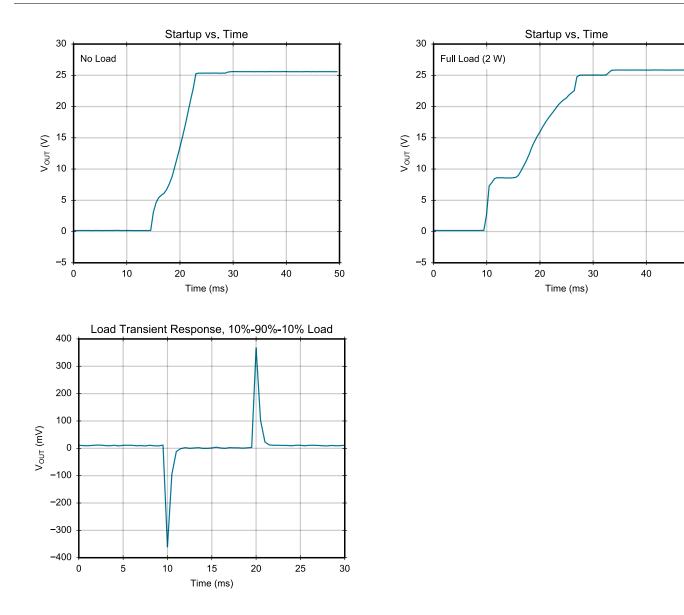

The dc-dc controller has an internal timer that controls the power conversion start-up to limit inrush current. There is also a Soft Start option where users can program the soft start up by an external capacitor connected to the SS pin.

The soft start period is the maximum duration of time that the Si8283/84 will try to ramp up the output voltage. If the output voltage fails to reach the targeted voltage level within this soft start period, the Si8283/84 will terminate the dc-dc startup cycle and wait for 40 seconds before initiating a new (startup) cycle.

The equations for setting the soft start period are as follows:

$$t_{SS} = 200000 \times C_{SS}$$

or

$$C_{SS} = \frac{t_{SS}}{200000}$$

#### 2.12.8 Programmable Frequency (Si8283 and Si8284 Only)

The frequency of the PWM modulator is set to a default of 250 kHz for Si828x. Users can program their desired frequency within a given band of 200 kHz to 800 kHz by controlling the time constant of an external RC connected to the SH\_FC and SS pins.

The equations for setting  $f_{SW}$  or  $R_{SW}$  are as follows:

$$f_{SW} = \frac{1025.5}{(R_{SW} \times C_{SS})}$$

or

$$R_{SW} = \frac{1025.5}{(f_{SW} \times C_{SS})}$$

The following are the recommended steps for calculating C<sub>SS</sub> and R<sub>SW</sub>:

1. Select the maximum soft start duration (typically 40 ms).

- 2. Calculate Css using Equation A.

- 3. Select the dc-dc switching frequency.

- 4. Calculate R<sub>SW</sub> using the above equation.

#### 2.12.9 Low Supply Voltage Configuration

The low supply voltage configuration is used when 3.0 V to 5.5 V supply rails are available. All product options of the Si8281 and Si8283 are intended for this configuration.

An advantage of Si828x devices over other converters that use this same topology is that the output voltage is sensed on the secondary side without requiring additional optocouplers and support circuitry to bias those optocouplers. This allows the dc-dc to operate with superior line and load regulation while reducing external components and increasing lifetime reliability.

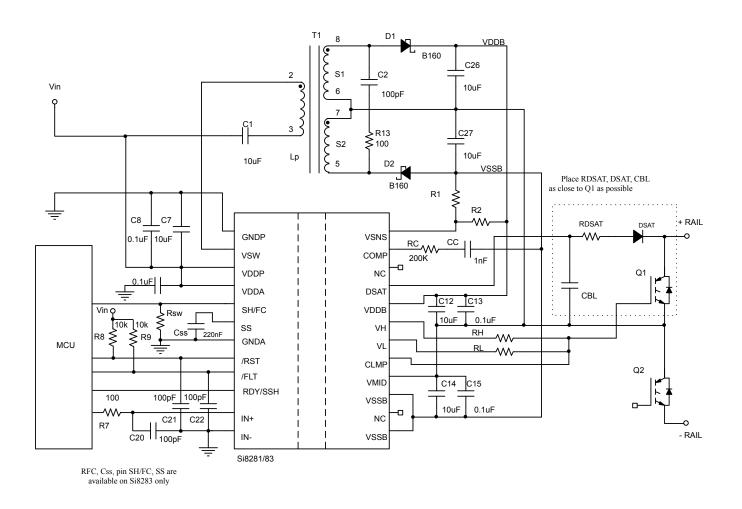

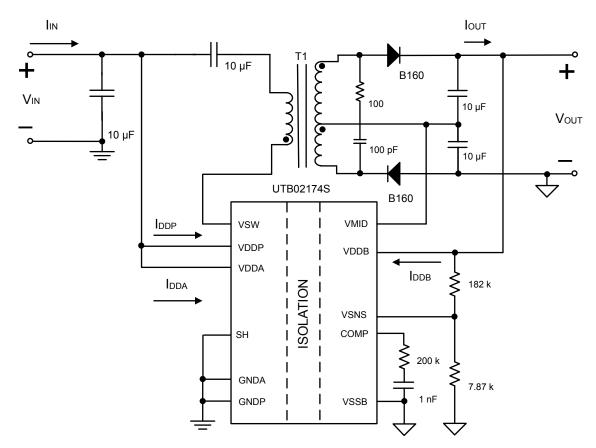

In a typical isolated gate driver application, the dc-dc powers the Si8281 and Si8283 VDDB and VSSB as shown in the figure below. The Si8281 and Si8283 dc-dc circuit in the figure below can deliver up to 2 W of output power for  $V_{in} = 5$  V and 1 W for  $V_{in} = 3.3$  V. The dc-dc requires an input capacitor, C<sub>2</sub>, blocking capacitor, C<sub>1</sub>, transformer, T<sub>1</sub>, rectifying diodes, D<sub>1</sub> and D<sub>2</sub>, and output capacitors, C<sub>26</sub>, and C<sub>27</sub>. Resistors R<sub>1</sub> and R<sub>2</sub> divide the output voltage to match the internal reference of the error amplifier. The ratio of the two secondary windings, S1 and S2, splits the output voltage into two portions. The positive VDDB and the negative VSSB with common reference to VMID (IGBT Emitter).

$$VDDB = VOUT \times \left(\frac{S1}{S1 + S2}\right)$$

$$VSSB = -VOUT \times \left(\frac{S2}{S1 + S2}\right)$$

Type 1 loop compensation made by RCOMP and CCOMP are required at the COMP pin. The combination of RCOMP = 200 k $\Omega$  and CCOMP = 1 nF satisfies most Si8281 and Si8283 dc-dc applications. Though it is not necessary for normal operation, we recommend that an RC snubber (not shown) be placed in parallel with the secondary winding to minimize radiated emissions.

Figure 2.5. Si8281/83 Block Diagram: 3 V–5 V Input to Split Voltage Output

#### 2.12.10 High Supply Voltage Configuration

2h

=.w..]6+\*28x9q\\-

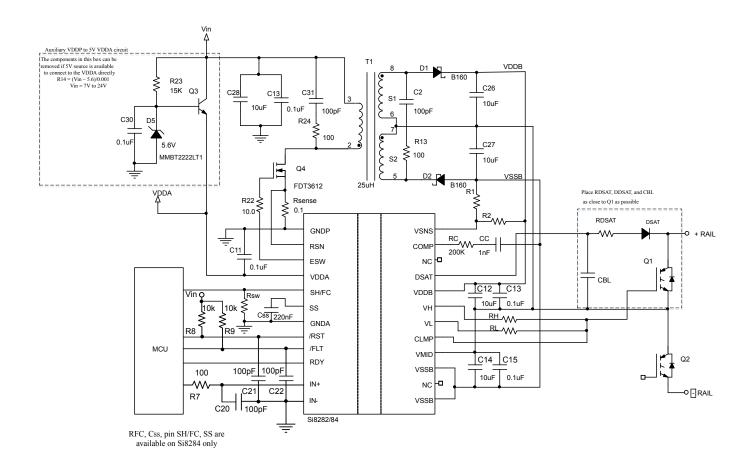

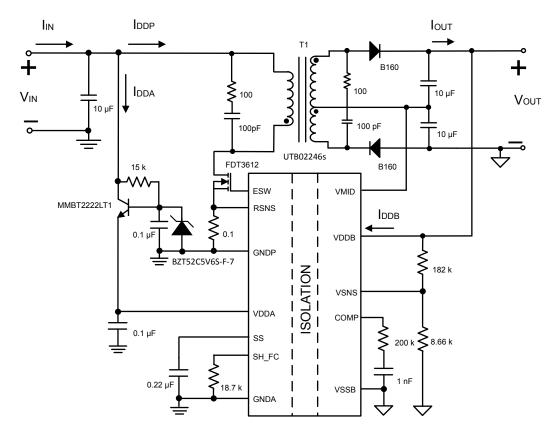

The high supply voltage configuration is used when a higher voltage power supply rail (up to 24 V) is available. All product options of the Si8282 and Si8284 are intended for this configuration. The dc-dc converter uses the isolated flyback topology. With this topology, the switch and sense resistor are external, allowing higher switching voltages.

The output voltage is sensed on the secondary side without requiring additional optocouplers and support circuitry to bias those optocouplers. This allows the dc-dc to operate with superior line and load regulation.

The figure below shows the block diagram of an Si828x with external components. The Si8284 product option has externally controlled switching frequency and soft start. The dc-dc requires input capacitor  $C_{28}$ , transformer  $T_1$ , switch  $Q_4$ , sense resistor  $R_{sense}$ , rectifying diodes  $D_1$  and  $D_2$ , and output capacitors  $C_{26}$  and  $C_{27}$ . To supply VDDA,  $Q_3$  transistor is biased by  $R_{23}$ , 5.6 V Zener diode  $D_5$  and filtered by  $C_{30}$  and  $C_{11}$ . External frequency and soft start behavior is set by CSS and RFSW. Resistors  $R_1$  and  $R_2$  divide the output voltage to match the internal reference of the error amplifier. The ratio of the two secondary windings splits the output voltage into two portions. The positive VDDB and the negative VSSB with common reference to VMID (IGBT Emitter).

$$VDDB = VOUT \times \left(\frac{S1}{S1 + S2}\right)$$

$$VSSB = -VOUT \times \left(\frac{S2}{S1 + S2}\right)$$

Type 1 loop compensation made by RCOMP and CCOMP are required at the COMP pin. The combination of RCOMP =  $49.9 \text{ k}\Omega$  and CCOMP = 1.5 nF satisfies most Si8282 and Si8284 dc-dc applications. Though it is not necessary for normal operation, we recommend to use RC snubbers (not shown) on both primary and secondary windings to minimize high-frequency emissions.

Figure 2.6. Si8282/84 Block Diagram: >5.5 V Input to Split Voltage Output

### 2.13 Transformer Design

The internal switch dc-dc (Si8281, Si8283) and external switch dc-dc (Si8282, Si8284) operate in different topologies and, thus, require different transformer designs. The table below provides a list of transformers and their parametric characteristics that have been validated to work with Si828x products. It is recommended that users order the transformers from the vendors per the part numbers given below.

To manufacture transformers from your preferred suppliers that may not be listed below, please specify to supplier the parametric characteristics as specified in the table below for a given input voltage and isolation rating.

| Transformer Supplier | Ordering Part # | Input<br>Voltage | Turns Ratio | Leakage    | Primary     | Primary     | Isolation |

|----------------------|-----------------|------------------|-------------|------------|-------------|-------------|-----------|

|                      |                 |                  |             | Inductance | Inductance  | Resistance  | Rating    |

| UMEC                 | UTB02257s       | 3.0–5.5 V        | 1:15:5      | 125 nH max | 1.5 µH ± 5% | 0.05 Ω max  | 5 kV      |

| www.umec-usa.com     | UTB02241s       | 4.5–5.5 V        | 1:9:33.667  | 100 nH max | 2 µH ± 5%   | 0.05 Ω max  | 5 kV      |

|                      | UTB02253s       | 7–24 V           | 1.2:1.21    | 200 nH max | 25 µH ± 5%  | 0.225 Ω max | 5 kV      |

| Coilcraft            | TA7788-AL       | 7–24 V           | 1:1.25:0.75 | 550 nH max | 25 µH ± 5%  | 0.460 Ω max | 5 kV      |

| www.coilcraft.com    |                 |                  |             |            |             |             |           |

#### Table 2.2. Si828x Recommended Transformers

## 3. Applications Information

The following sections detail the input and output circuits necessary for proper operation.

### 3.1 Recommended Application Circuits

Figure 3.1. Recommended Si8281/83 Application Circuit

#### Figure 3.2. Recommended Si8282/84 Application Circuit

The Si828x has both inverting and non-inverting gate control inputs (IN– and IN+). In normal operation, one of the inputs is not used, and should be connected to GNDA (IN–) or VDDA (IN+) for proper logic termination. The Si828x has an active low reset input (RSTb), an active high ready (RDY) push pull output, and an open drain fault (FLTb) output that requires a weak 10 k $\Omega$  pull-up resistor. The Si828x gate driver will shut down when a fault is detected. It then provides FLTb indication to the MCU, and remains in the shutdown state until the MCU applies a reset signal.

The desaturation sensing circuit consisted of the 380 pF blanking capacitor, 100  $\Omega$  current limiting resistor, and DSAT diode. These components provide current and voltage protection for the Si828x desaturation DSAT pin and it is critical to place these components as close to the IGBT as possible. Also, on the layout, make sure that the loop area forming between these components and the IGBT be minimized for optimum desaturation detection. The Si828x has VH and VL gate drive outputs with external RH and RL resistors to limit output gate current. The value of these resistors can be adjusted to independently control IGBT collector voltage rise and fall time. The CLMP output should be connected to the gate of the IGBT directly to provide clamping action between the gate and VSSB. This clamping action dissipates IGBT Miller current from collector to the gate to secure the IGBT in the off-state.

#### 3.1.1 Inputs

Inputs should be driven by CMOS level push-pull output. If input is driven by the MCU GPIO, it is recommended that the MCU be located as closed to the Si828x as possible to minimize PCB trace parasitic and noise coupling to the input circuit. In noisy environments, it is customary to add a small series resistor, and a decoupling cap to the IN traces (R7, C20 in Figure 3.1 Recommended Si8281/83 Application Circuit on page 11 and Figure 3.2 Recommended Si8282/84 Application Circuit on page 12). These RC filters attenuate glitches from electrical noise and improve input-to-output signal integrity.

#### 3.1.2 Reset, RDY, and Fault

The Si828x has an active high ready (RDY) push pull output, an open drain fault (FLTb) output, and an active low reset input (RSTb) that require pull-up resistors (R8 and R9). Fast common-mode transients in high-power circuits can inject noise and glitches into these pins due to parasitic coupling. Depending on the IGBT power circuit layout, additional capacitance (use 100 pF to 470 pF for C21 and C22) can be included on these pins to prevent faulty RDY and FLTb indications as well as unintended reset to the device.

The FLTb outputs from multiple Si828x devices can be connected in an OR wiring configuration to provide a single FLTb signal to the MCU.

#### 3.1.3 Desaturation

The desaturation sensing circuit consists of the blanking capacitor (390 pF recommended), 100  $\Omega$  current limiting resistor, and DSAT diode. These components provide current and voltage protection for the Si828x desaturation DSAT pin, and it is critical to place these components as close to the IGBT as possible. Also, in the layout, the loop area forming between these components and the IGBT should be minimized for optimum desaturation detection.

#### 3.1.4 Driver Outputs

The Si828x has VH and VL gate drive outputs (see Figure 3.1 Recommended Si8281/83 Application Circuit on page 11). They work with external RH and RL resistors to limit output gate current. The value of these resistors can be adjusted to independently control IGBT collector voltage rise and fall time.

The CLMP output should be connected to the gate of the IGBT directly to provide clamping action between the gate and VSSB pin. This clamping action dissipates IGBT Miller current from the collector to the gate to secure the IGBT in the off-state. Negative VSSB provides further help to ensure the gate voltage stays below the IGBT's Vth during the off state.

#### 3.2 Layout Considerations

It is most important to minimize ringing in the drive path and noise on the supply lines. Care must be taken to minimize parasitic inductance in these paths by locating the Si828x as close as possible to the device it is driving. In addition, the supply and ground trace paths must be kept short. For this reason, the use of power and ground planes is highly recommended. A split ground plane system having separate ground and power planes for power devices and small signal components provides the best overall noise performance.

### 3.3 Power Dissipation Considerations

Proper system design must assure that the Si828x operates within safe thermal limits across the entire load range. The Si828x total power dissipation is the sum of the power dissipated by bias supply current, internal parasitic switching losses, and power dissipated by the series gate resistor and load. Equation 1 shows total Si828x power dissipation.

$$PD = (VDDA)(IDDA) + 1.05(VDDB)(IDDB) + 1.05 \times f \times Q_{int} \times VDDB + \frac{1.05}{2}(f)(Q_{IGBT})(VDDB) \left[\frac{Rp}{Rp + RH} + \frac{Rn}{Rn + RL}\right]$$

where:

PD is the total Si828x device power dissipation (W).

IDDA is the input-side maximum bias current (7.5 mA).

IDDB is the driver die maximum bias current (10.8 mA).

Q<sub>int</sub> is the internal parasitic charge (3 nC).

VDDA is the input-side VDD supply voltage (2.7 to 5.5 V).

VDDB is the total driver-side supply voltage (VDDB + VSSB: 12.5 to 30 V).

f is the IGBT switching frequency (Hz).

RH is the VH external gate resistor, RL is the VL external gate resistor.

Rp is the RDS<sub>(ON)</sub> of the driver pull-up switch: (2.6  $\Omega$ ).

Rn is the RDS<sub>(ON)</sub> of the driver pull-down switch:  $(0.8 \Omega)$ .

#### Equation 1.

To account for the Si828x dc-dc loss, an additional 5% of power is added to the driver-side circuit (VDDB). The maximum power dissipation allowable for the Si828x is a function of the package thermal resistance, ambient temperature, and maximum allowable junction temperature, as shown in Equation 2:

$$PD$$

max  $\leq \frac{Tjmax - TA}{\theta ja}$

where:

PDmax = Maximum Si828x power dissipation (W).

Tjmax = Si828x maximum junction temperature (150 °C).

TA = Ambient temperature (°C)

$\theta$ ja = Si828x junction-to-air thermal resistance (60 °C/W for four-layer PCB)

f = Si828x switching frequency (Hz)

### Equation 2.

Substituting values for PDmax Tjmax (150 °C), TA (125 °C), and θja (60 °C/W) into Equation 2 results in a maximum allowable total power dissipation of 0.42 W.

$PD\max \leq \frac{150 - 125}{60} = 0.42W$

Maximum allowable load is found by substituting this limit and the appropriate data sheet values from Table 4.1 into Equation 1 and simplifying. The result is Equation 3.

$$PD = (VDDA)(IDDA) + 1.05(VDDB)(IDDB) + 1.05 \times f \times Qint \times VDDB + \frac{1.05}{2}(f)(Q_L)(VDDB)\left[\frac{Rp}{Rp + RH} + \frac{Rn}{Rn + RL}\right]$$

$$PD = (VDDA)(IDDA) + 1.05(VDDB)(IDDB) + 1.05 \times f \times Qint \times VDDB + \frac{1.05}{2}(f)(C_L)(VDDB^2)\left[\frac{Rp}{Rp + RH} + \frac{Rn}{Rn + RL}\right]$$

$$0.42 = (VDDA)(0.0075) + 1.05(VDDB)(0.0108) + 1.05 \times f \times 3 \times 10^{-9} \times VDDB + \frac{1.05}{2}(f)(C_L)(VDDB^2)\left[\frac{2.6}{2.6 + 15} + \frac{0.8}{0.8 + 10}\right]$$

$$0.42 - (VDDA)(0.0075) - 1.05(VDDB)(0.0108) - 1.05 \times f \times 3 \times 10^{-9} \times VDDB = 0.117VDDB^2f(C_L)$$

$$C_L = \frac{0.42 - (VDDA \times 7.5 \times 10^{-3}) - (VDDB \times 10.8 \times 10^{-3})}{C_L} - \frac{2.692 \times 10^{-8}}{2}$$

$$C_{L} = \frac{0.42 - (VDDA \times 7.5 \times 10^{\circ}) - (VDDB \times 10.8 \times 10^{\circ})}{0.117 \times VDDB^{2}(f)} - \frac{2.692 \times 10^{\circ}}{VDDB}$$

### Equation 3.

Below is an example power dissipation calculation for the Si828x driver using Equation 1 with the following givens:

$$V_{DDA} = 5.0 V$$

$$V_{DDB} = 18 V$$

$$f = 30 kHz$$

$$R_{H} = 10 \Omega$$

$$R_{L} = 15 \Omega$$

$$Q_{G} = 85 nC$$

$PD = (5)(0.0075) + 1.05(18)(0.0108) + 1.05(2 \times 10^{4})(3 \times 10^{-9})(18) + \frac{1.05}{2}(3 \times 10^{4})(85 \times 10^{-9})(18)\left[\frac{2.6}{2.6 + 10} + \frac{0.8}{0.8 + 15}\right] = 242mW$

The driver junction temperature is calculated using Equation 2, where:

Pd is the total Si828x device power dissipation (W)

θja is the thermal resistance from junction to air (60 °C/W in this example)

TA is the maximum ambient temperature (125 °C)

$$Tj = Pd \times \theta ja + TA$$

$Tj = (0.242) \times (60) + 125 = 139.5^{\circ}C$

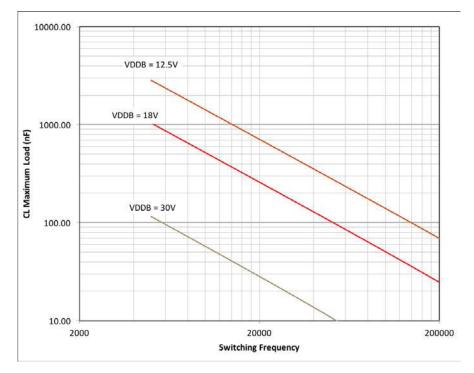

Calculate maximum loading capacitance from equation 3:

1. VDDA = 5 V and (VDDB–VSSB) = 12.5 V.

$$C_L = \frac{1.51 \times 10^{-2}}{f} - 2.15 \times 10^{-9}$$

2. VDDA = 5 V and (VDDB-VSSB) = 18 V.

$$C_L = \frac{5.91 \times 10^{-3}}{f} - 1.5 \times 10^{-9}$$

3. VDDA = 5 V and (VDDB-VSSB) = 30 V.

$$C_L = \frac{1.04 \times 10^{-3}}{f} - 8.97 \times 10^{-10}$$

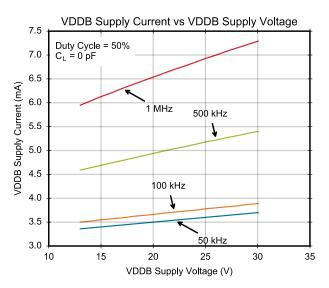

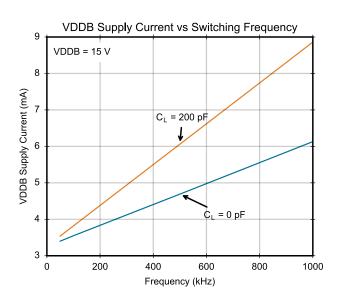

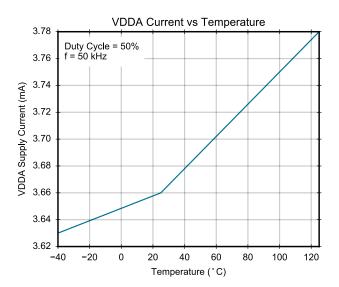

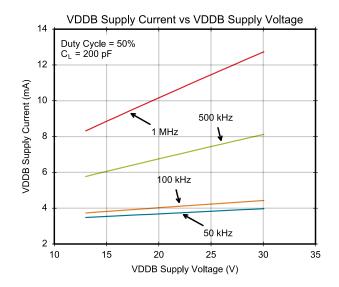

Graphs are shown in the following figure. All points along the load lines in these graphs represent the package dissipation-limited value of C<sub>L</sub> for the corresponding switching frequency.

Figure 3.3. Maximum Load vs. Switching Frequency (25 °C)

# 4. Electrical Specifications

### Table 4.1. Electrical Specifications

$V_{IN}$  = 24 V;  $V_{DDA}$  = 4.3 V (See Figure 3) for all Si8282/84;  $V_{DDA}$  =  $V_{DDP}$  = 3.0 to 5.0 V (See Figure 2) for all Si8281/83;  $T_A$  = -40 to +125 °C unless otherwise noted.

| Parameter                          | Symbol               | Test Condition                                  | Min   | Тур  | Max   | Units  |

|------------------------------------|----------------------|-------------------------------------------------|-------|------|-------|--------|

| DC Parameters                      |                      |                                                 |       |      |       |        |

| Input Supply Voltage               | VDDA                 |                                                 | 2.8   | _    | 5.5   | V      |

| Power Input Voltage                | VDDP                 |                                                 | 3.0   | _    | 5.5   | V      |

|                                    | (VDDB – VSSB)        |                                                 | 9.5   | _    | 30    | V      |

| Driver Supply Voltage              | (VMID – VSSB)        |                                                 | 0     | _    | 15    | V      |

| Input Supply Quiescent Current     | IDDA(Q)              |                                                 | _     | 6.8  | 7.5   | mA     |

| Input Supply Active Current        | IDDA                 | f = 10 kHz                                      | _     | 10.5 | _     | mA     |

| Output Supply Quiescent Current    | IDDB(Q)              |                                                 | _     | 8.7  | 10.8  | mA     |

| DC-DC Converter                    |                      |                                                 |       | 1    |       |        |

| Switching Frequency Si8281, Si8282 | FSW                  |                                                 | _     | 250  | _     | kHz    |

|                                    |                      | RFSW = 23.3 kΩ                                  |       |      |       |        |

|                                    |                      | FSW = 1025.5/(RFSW x CSS)                       | 180   | 200  | 220   | kHz    |

|                                    |                      | CSS = 220 nF<br>(1% tolerance on BOM)           | 100   | 200  |       |        |

|                                    | 50.07                | RFSW = 9.3 kΩ                                   |       |      |       |        |

| Switching Frequency Si8283, Si8284 | FSW                  | FSW = 1025.5/(RFSW x CSS)                       | 450   | 500  | 550   | kHz    |

|                                    |                      | CSS = 220 nF<br>(1% tolerance on BOM)           |       |      |       |        |

|                                    |                      | RFSW = 5.18 kΩ                                  | 040   | 000  |       |        |

|                                    |                      | CSS = 220 nF                                    | 810   | 900  | 990   | kHz    |

| VSNS Voltage                       | VSNS                 |                                                 | 1.002 | 1.05 | 1.097 | V      |

| VSNS Current Offset                | I <sub>offset</sub>  | ILOAD = 0 A                                     | -500  | _    | 500   | nA     |

| Output Voltage Accuracy            |                      | ILOAD = 0 mA                                    | -5    | _    | +5    | %      |

|                                    | ΔVOUT(line)/         | ILOAD = 50 mA                                   |       |      |       |        |

| Line Regulation                    | ΔVDDP                | VDDP varies from 4.5 to 5.5 V                   | —     | 1    | _     | mV/V   |

| Load Regulation                    | ΔVOUT(load)/<br>VOUT | ILOAD = 50 to 400 mA                            | _     | 0.1  | _     | %      |

| Output Voltage Ripple              |                      |                                                 |       |      |       |        |

| Si8281, Si8283                     |                      | ILOAD = 100 mA                                  | —     | 100  | _     | mV p-p |

| Si8282, Si8284                     |                      |                                                 |       |      |       |        |

| Turn-on overshoot                  | ΔVOUT(start)         | CIN = COUT = 0.1 μF in paral-<br>lel with 10 μF | _     | 2    |       | %      |

|                                    |                      | ILOAD = 0 A                                     |       |      |       |        |

| Parameter                             | Symbol              | Test Condition                   | Min | Тур  | Мах | Units |

|---------------------------------------|---------------------|----------------------------------|-----|------|-----|-------|

| Continuous Output Current             |                     |                                  |     |      |     |       |

| Si8281, Si8283                        |                     |                                  |     |      |     |       |

| 5.0 V to 5.0 V                        |                     |                                  |     | 200  |     |       |

| 3.3 V to 3.3 V                        |                     |                                  |     | 400  |     |       |

| 3.3 V to 5.0 V                        | ILOAD(max)          |                                  |     | 250  |     | mA    |

| Si8282, Si8284                        |                     |                                  |     |      |     |       |

| 24 V to 5.0 V                         |                     |                                  |     | 1000 |     |       |

| 24 V to 3.0 V                         |                     |                                  |     | 1500 |     |       |

| Cycle-by-Cycle Average Current Limit  |                     |                                  |     |      |     |       |

| Si8281, Si8283                        | ILIM                | Output short circuited           | _   | 3    | _   | A     |

| No-Load Supply Current IDDP           |                     |                                  |     |      |     |       |

| Si8281, Si8283                        | IDDPQ_DCDC          | VDDP = VDDA = 5 V                | _   | 30   | -   | mA    |

| No-Load Supply Current IDDA           |                     |                                  |     |      |     |       |

| Si8281, Si8283                        | IDDAQ_DCDC          | VDDP = VDDA = 5 V                | _   | 5.7  | _   | mA    |

| No-Load Supply Current IDDP           |                     |                                  |     |      |     |       |

| Si8282, Si8284                        | IDDPQ_DCDC          | VIN = 24 V                       | _   | 0.8  | _   | mA    |

| No-Load Supply Current IDDA           |                     |                                  |     |      |     |       |

| Si8282, Si8284                        | IDDAQ_DCDC          | VIN = 24 V                       | _   | 5.8  | _   | mA    |

| Peak Efficiency                       |                     |                                  |     |      |     |       |

| Si8281, Si8283                        | η                   |                                  | _   | 78   | _   | %     |

| Si8282, Si8284                        |                     |                                  |     | 83   |     |       |

| Soft Start Time, Full Load            |                     |                                  |     |      |     |       |

| Si8281, Si8282                        | t <sub>SST</sub>    |                                  | _   | 25   | _   | ms    |

| Si8283, Si8284                        |                     |                                  |     | 50   |     |       |

| Restart Delay from Fault Event        | t <sub>OTP</sub>    |                                  |     | 21   | _   | s     |

| Drive Parameters                      |                     |                                  |     | 1    |     | 1     |

| High Drive Transistor RDS(ON)         | R <sub>OH</sub>     |                                  |     | 2.48 | _   | Ω     |

| Low Drive Transistor RDS(ON)          | R <sub>OL</sub>     |                                  | _   | 0.86 | _   | Ω     |

|                                       |                     | VH = VDDB – 15 V                 |     |      |     |       |

| High Drive Peak Output Current        | I <sub>ОН</sub>     | $T_{PW\_IOH} \le 250 \text{ ns}$ | 2.5 | 2.8  | _   | A     |

|                                       |                     | VL = VSSB + 6.0 V                |     |      |     |       |

| Low Drive Peak Output Current         | I <sub>OL</sub>     | T <sub>PW_IOL</sub> ≤ 250 ns     | 3.0 | 3.4  | _   | A     |

| UVLO Parameters                       |                     |                                  |     |      |     |       |

| UVLO Threshold +                      | VDDA <sub>UV+</sub> |                                  | 2.4 | 2.7  | 3.0 |       |

| UVLO Threshold –                      | VDDA <sub>UV-</sub> |                                  | 2.3 | 2.6  | 2.9 |       |

| UVLO Lockout Hysteresis- (Input Side) | VDDA <sub>HYS</sub> |                                  |     | 100  | _   | mV    |

Si8281/82/83/84 Data Sheet Electrical Specifications

| Parameter                                             | Symbol                    | Test Condition                            | Min        | Тур  | Мах  | Units |

|-------------------------------------------------------|---------------------------|-------------------------------------------|------------|------|------|-------|

| UVLO Threshold + (Driver Side)                        |                           |                                           |            |      |      |       |

| 9 V Threshold (Si828xBD)                              | VDDB <sub>UV+</sub>       |                                           | 8.0        | 9.0  | 10.0 | V     |

| 12 V Threshold (Si828xCD)                             |                           |                                           | 10.8       | 12.0 | 13.2 | V     |

| UVLO Threshold – (Driver Side)                        |                           |                                           |            |      |      |       |

| 9 V Threshold (Si828xBD)                              | VDDB <sub>UV-</sub>       |                                           | 7.0        | 8.0  | 9.0  | V     |

| 12 V Threshold (Si828xCD)                             |                           |                                           | 9.8        | 11.0 | 12.2 | V     |

| UVLO lockout hysteresis (Driver Side)                 | VDDB <sub>HYS</sub>       |                                           | _          | 1    | _    | V     |

| UVLO+ to RDY High Delay                               | t <sub>UVLO+ to RDY</sub> |                                           | _          |      | 100  | μs    |

| ULVO– to RDY Low Delay                                | t <sub>UVLO-</sub> to RDY |                                           | _          |      | 0.79 | μs    |

| Desaturation Detector Parameters                      |                           |                                           |            |      |      |       |

| DESAT Threshold                                       | VDESAT                    | VDDB – VSSB ><br>VDDBUV+                  | 6.5        | 6.9  | 7.3  | v     |

| C <sub>BI</sub> charging current                      | I <sub>Chg</sub>          |                                           | _          | 1    |      | mA    |

| DESAT Sense to 90% VOUT Delay                         | t <sub>DESAT(90%)</sub>   |                                           | _          | 220  | 300  | ns    |

| DESAT Sense to 10% VOUT Delay                         | t <sub>DESAT(10%)</sub>   |                                           | 0.77       | 2.5  | 2.7  | μs    |

| DESAT Sense to FLT Low Delay                          | tDESAT to FLT             |                                           | _          | 220  | 300  | ns    |

| Reset to FLT High Delay                               | t <sub>RST to FLT</sub>   |                                           | _          | 37   | 45   | ns    |

| Miller Clamp Parameters (Si8285 Only)                 |                           |                                           |            |      |      |       |

| Clamp Pin Threshold Voltage                           | V <sub>t</sub> Clamp      |                                           | _          | 2.0  | _    | V     |

| Miller Clamp Transistor RDS (ON)                      | R <sub>MC</sub>           |                                           | _          | 1.07 | _    | Ω     |

| Clamp Low Level Sinking Current                       | I <sub>CL</sub>           | VCLMP = VSSB + 6.0                        | 3.0        | 3.4  | _    | Α     |

| Digital Parameters                                    |                           |                                           |            |      |      | I     |

| Logic High Input Threshold                            | VIH                       |                                           | 2.0        | _    | _    | V     |

| Logic Low Input Threshold                             | VIL                       |                                           | _          |      | 0.8  | V     |

| Input Hysteresis                                      | VIHYST                    |                                           | _          | 440  | _    | mV    |

| High Level Output Voltage (RDY pin on-<br>ly)         | VOH                       | IO = -4 mA                                | VDDA – 0.4 | _    | _    | V     |

| Low Level Output Voltage (RDY pin on-<br>ly)          | VOL                       | IO = 4 mA                                 | _          |      | 0.4  | V     |

| Open-Drain Low Level Output Voltage<br>(FLT pin only) |                           | VDDA = 5 V,<br>5 kΩ pull-up resistor      | _          | _    | 200  | mV    |

| AC Switching Parameters                               |                           |                                           |            |      |      |       |

| Propagation Delay (Low-to-High)                       | t <sub>PLH</sub>          | CL = 200 pF                               | 30         | 40   | 50   | ns    |

| Propagation Delay (High-to-Low)                       | t <sub>PHL</sub>          | CL = 200 pF                               | 30         | 40   | 50   | ns    |

| Pulse Width Distortion                                | PWD                       | t <sub>PLH</sub> – t <sub>PHL</sub>       |            | 1    | 5    | ns    |

|                                                       | PDD                       | t <sub>PHLMAX</sub> – t <sub>PLHMIN</sub> | -1         |      | 25   | ns    |

| Propagation Delay Difference <sup>4</sup>             | 100                       |                                           |            |      | 20   | 110   |

| Parameter                      | Symbol         | Test Condition                      | Min | Тур | Мах | Units |

|--------------------------------|----------------|-------------------------------------|-----|-----|-----|-------|

| Fall Time                      | t <sub>F</sub> | CL = 200 pF                         | —   | 8.5 | 20  | ns    |

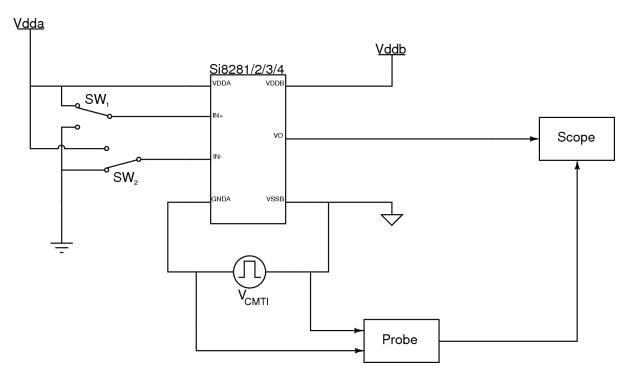

| Common Mode Transient Immunity |                | Output = low or high (VCM = 1500 V) | 35  | 50  | _   | kV/µs |

1. See Ordering Guide for more information.

2. Minimum value of (VDD – GND) decoupling capacitor is 1  $\mu$ F.

3. When performing this test, it is recommended that the DUT be soldered to avoid trace inductances, which may cause overstress conditions.

4. Guaranteed by characterization.

Figure 4.1. Si8281, Si8283 Measurement Circuit for Converter Efficiency and Regulation

Figure 4.2. Si8282, Si8284 Measurement Circuit for Converter Efficiency and Regulation

Figure 4.3. Common-Mode Transient Immunity Characterization Circuit

| Parameter                                                                | Symbol           | Min  | Мах  | Unit             |

|--------------------------------------------------------------------------|------------------|------|------|------------------|

| Storage Temperature                                                      | T <sub>STG</sub> | -65  | +150 | °C               |

| Operating Temperature                                                    | T <sub>A</sub>   | -40  | +125 | °C               |

| Junction Temperature                                                     | TJ               | _    | +140 | °C               |

| Peak Output Current (t <sub>PW</sub> = 10 µs)                            | I <sub>OPK</sub> | _    | 4.0  | А                |

| Supply Voltage                                                           | VDD              | -0.5 | 36   | V                |

| Output Voltage                                                           | V <sub>OUT</sub> | -0.5 | 36   | V                |

| Input Power Dissipation                                                  | PI               | _    | 100  | mW               |

| Output Power Dissipation                                                 | Po               | _    | 800  | mW               |

| Total Power Dissipation (All Packages Limited by Thermal Derating Curve) | PT               | _    | 900  | mW               |

| Lead Solder Temperature (10 s)                                           |                  | _    | 260  | °C               |

| HBM Rating ESD                                                           |                  | 4    | —    | kV               |

| Machine Model ESD                                                        |                  | 300  | _    | V                |

| CDM                                                                      |                  | 2000 | —    | V                |

| Maximum Isolation (Input to Output) (1 sec) WB SOIC-16                   |                  | _    | 6500 | V <sub>RMS</sub> |

### Table 4.2. Absolute Maximum Ratings<sup>1</sup>

Note:

1. Permanent device damage may occur if the absolute maximum ratings are exceeded. Functional operation should be restricted to the conditions as specified in the operational sections of this data sheet. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### 4.1 Timing Diagrams

Figure 4.5. Device Reaction to Desaturation Event

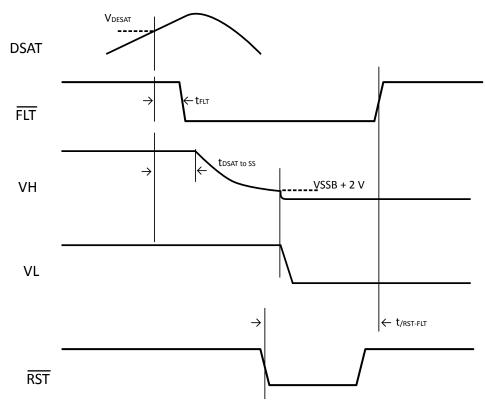

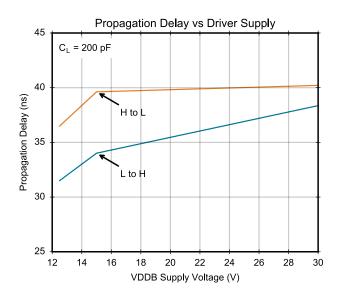

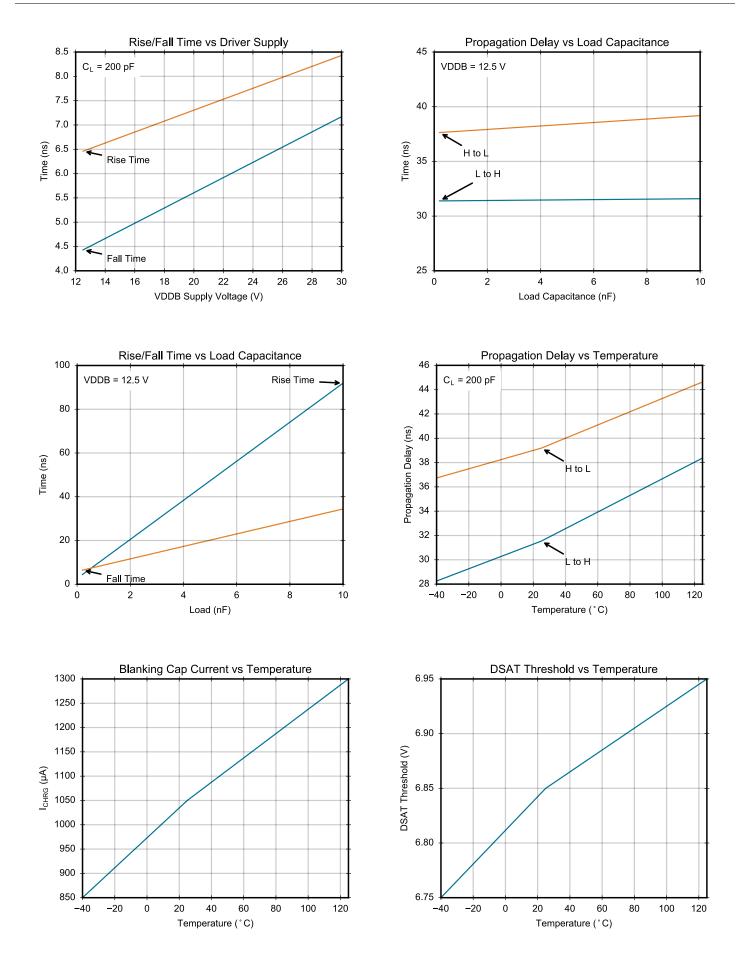

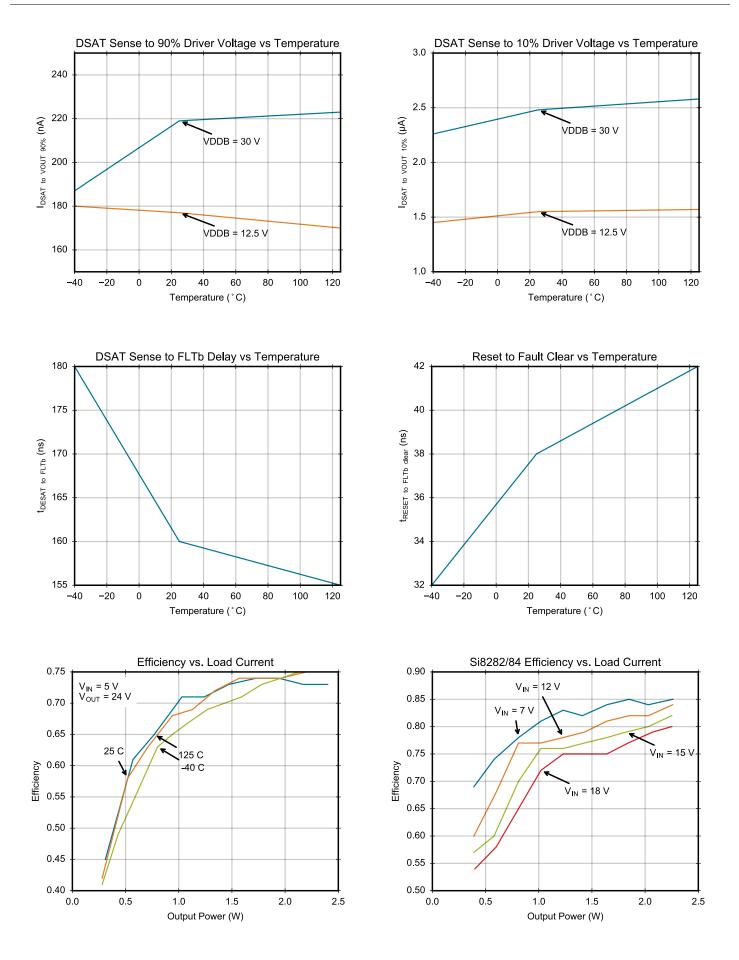

### 4.2 Typical Operating Characteristics

50

### 4.3 Regulatory Information

### Table 4.3. Regulatory Information<sup>1, 2</sup>

### CSA

The Si828x is certified under CSA Component Acceptance Notice 5A. For more details, see File 232873.

60950-1: Up to 600 V<sub>RMS</sub> reinforced insulation working voltage; up to 1000 V<sub>RMS</sub> basic insulation working voltage.

### VDE

The Si828x is certified according to VDE0884. For more details, see File 5006301-4880-0001.

VDE 0884-10: Up to 1414 V<sub>peak</sub> for reinforced insulation working voltage.

### UL

The Si828x is certified under UL1577 component recognition program. For more details, see File E257455.

Rated up to 5000  $V_{\mbox{RMS}}$  isolation voltage for basic protection.

### CQC

The Si828x is certified under GB4943.1-2011.

Rated up to 600 V<sub>RMS</sub> reinforced insulation working voltage; up to 1000 V<sub>RMS</sub> basic insulation working voltage.

### Note:

1. Regulatory Certifications apply to 5.0 kV<sub>RMS</sub> rated devices, which are production tested to 6.0 kV<sub>RMS</sub> for 1 sec.

2. For more information, see 1. Ordering Guide.

### Table 4.4. Insulation and Safety-Related Specifications

| Parameter                                  | Symbol          | Test Condition | Value            | Unit |

|--------------------------------------------|-----------------|----------------|------------------|------|

|                                            |                 |                | WB SOIC          |      |

| Nominal Air Gap (Clearance) <sup>1</sup>   | L(101)          |                | 8.0              | mm   |

| Nominal External Tracking (Creepage)       | L(102)          |                | 8.0              | mm   |

| Minimum Internal Gap (Internal Clearance)  |                 |                | 0.016            | mm   |

| Tracking Resistance (Proof Tracking Index) | PTI             | IEC60112       | 600              | V    |

| Erosion Depth                              | ED              |                | 0.019            | mm   |

| Resistance (Input-Output) <sup>2</sup>     | R <sub>IO</sub> |                | 10 <sup>12</sup> | Ω    |

| Capacitance (Input-Output) <sup>2</sup>    | C <sub>IO</sub> | f = 1 MHz      | 1                | pF   |

### Note:

1. The values in this table correspond to the nominal creepage and clearance values as detailed in 6.1 Package Outline: 20-Pin Wide Body SOIC and 6.3 Package Outline: 24-Pin Wide Body SOIC. VDE certifies the clearance and creepage limits as 8.5 mm minimum for the WB SOIC-16. UL does not impose a clearance and creepage minimum for component level certifications. CSA certifies the clearance and creepage limits as 7.6 mm minimum for the WB SOIC-16 package.

2. To determine resistance and capacitance, the Si828x is converted into a 2-terminal device. Pins 1–8 are shorted together to form the first terminal, and pins 9–16 are shorted together to form the second terminal. The parameters are then measured between these two terminals.

### Table 4.5. IEC 60664-1 Ratings

| Parameter                   | Test Condition                              | Specification |

|-----------------------------|---------------------------------------------|---------------|

|                             |                                             | WB SOIC       |

| Basic Isolation Group       | Material Group                              | I             |

| Installation Classification | Rated Mains Voltages ≤ 150 V <sub>RMS</sub> | I-IV          |

|                             | Rated Mains Voltages ≤ 300 V <sub>RMS</sub> | I-IV          |

|                             | Rated Mains Voltages ≤ 600 V <sub>RMS</sub> | 1-111         |

### Table 4.6. IEC 60747-5-5 (VDE 0884 Part 10) Insulation Characteristics<sup>1</sup>

| Parameter                                         | Symbol            | Test Condition                                                                                                                           | Characteristic   | Unit    |

|---------------------------------------------------|-------------------|------------------------------------------------------------------------------------------------------------------------------------------|------------------|---------|

|                                                   |                   |                                                                                                                                          | WB SOIC          |         |

| Maximum Working Insulation Voltage                | VIORM             |                                                                                                                                          | 1414             | V peak  |

| Input to Output Test Voltage                      | V <sub>PR</sub>   | Method b1 (V <sub>IORM</sub> x 1.875 = V <sub>PR</sub> , 100%<br>Production Test, t <sub>m</sub> = 1 sec, Partial Dis-<br>charge < 5 pC) | 2652             | V peak  |

| Transient Overvoltage                             | V <sub>IOTM</sub> | t = 60 sec                                                                                                                               | 8000             | V peak  |

| Surge Voltage                                     | V <sub>IOSM</sub> | Tested per IEC 60065 with surge voltage of 1.2 $\mu$ s/50 $\mu$ s with magnitude 6250 V x 1.6 = 10 kV                                    | 6250             | kV peak |

| Pollution Degree (DIN VDE 0110, See Table XX.)    |                   |                                                                                                                                          | 2                |         |

| Insulation Resistance at $T_S$ , $V_{IO}$ = 500 V | R <sub>S</sub>    |                                                                                                                                          | >10 <sup>9</sup> | Ω       |

### Note:

1. This isolator is suitable for reinforced electrical isolation only within the safety limit data. Maintenance of the safety data is ensured by protective circuits. The Si828x provides a climate classification of 40/125/21.

### Table 4.7. IEC Safety Limiting Values<sup>1</sup>

| Parameter                      | Symbol         | Test Condition                                                                                     | Мах        |            | Unit |

|--------------------------------|----------------|----------------------------------------------------------------------------------------------------|------------|------------|------|

|                                |                |                                                                                                    | WB SOIC-20 | WB SOIC-24 |      |

| Case Temperature               | T <sub>S</sub> |                                                                                                    | 150        | 150        | °C   |

| Input Current                  | I <sub>S</sub> | $\theta_{JA}$ = 60 °C/W (WB SOIC-20 or SOIC-24)<br>T <sub>J</sub> = 140 °C, T <sub>A</sub> = 25 °C | 30         | 30         | mA   |

| Output Power                   | Ps             |                                                                                                    | 0.9        | 0.9        | W    |

| Note:<br>1. Maximum value allo | wed in the     | event of a failure.                                                                                | 1          |            |      |

### Table 4.8. Thermal Characteristics

| Parameter                             | Symbol          | Тур        |            | Unit |

|---------------------------------------|-----------------|------------|------------|------|

|                                       |                 | WB SOIC-20 | WB SOIC-24 |      |

| IC Junction-to-Air Thermal Resistance | θ <sub>JA</sub> | 60         | 60         | °C/W |

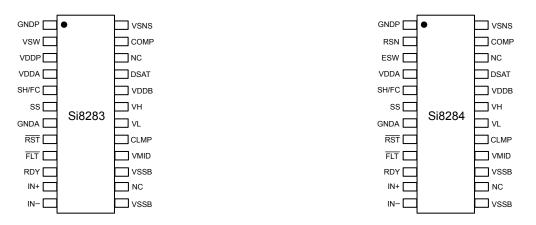

# 5. Pin Descriptions

### Table 5.1. Si8281/82 Pin Descriptions

| Name            | Si8281 Pin # | Si8282 Pin # | Description                          |  |

|-----------------|--------------|--------------|--------------------------------------|--|

| GNDP            | 1            | 1            | Power stage ground                   |  |

| VSW             | 2            | —            | Power stage internal switch          |  |

| RSN             | _            | 2            | Power stage current sense            |  |

| VDDP            | 3            | —            | Power stage supply                   |  |

| ESW             | _            | 3            | Power stage external switch drive    |  |

| VDDA            | 4            | 4            | Input side low voltage power supply  |  |

| GNDA            | 5            | 5            | Input side low voltage ground        |  |

| RSTb            | 6            | 6            | Reset fault condition                |  |

| FLTb            | 7            | 7            | Fault condition signal               |  |

| RDY             | 8            | 8            | UVLO ready signal                    |  |

| IN+             | 9            | 9            | Driver control plus                  |  |

| IN–             | 10           | 10           | Driver control minus                 |  |

| VSSB            | 11           | 11           | Output side low voltage power supply |  |

| VMID            | 12           | 12           | Drain reference for driven switch    |  |

| CLMP            | 13           | 13           | Miller clamp                         |  |

| VL              | 14           | 14           | Low gate drive                       |  |

| VH              | 15           | 15           | High gate drive                      |  |

| VDDB            | 16           | 16           | Output side low voltage power supply |  |

| DSAT            | 17           | 17           | Desaturation detection input         |  |

| NC <sup>1</sup> | 18           | 18           | No connect                           |  |

| COMP            | 19           | 19           | dc/dc compensation                   |  |

| VSNS            | 20           | 20           | dc/dc voltage feedback               |  |

Note:

1. No Connect. These pins are not internally connected. To maximize CMTI performance, these pins should be connected to the ground plane.

### Table 5.2. Si8283/84 Pin Descriptions

| Name            | Si8283 Pin # | Si8284 Pin # | Description                           |

|-----------------|--------------|--------------|---------------------------------------|

| GNDP            | 1            | 1            | Power stage ground                    |

| VSW             | 2            | _            | Power stage internal switch           |

| RSN             | _            | 2            | Power stage current sense             |

| VDDP            | 3            | _            | Power stage supply                    |

| ESW             | _            | 3            | Power stage external switch drive     |

| VDDA            | 4            | 4            | Input side low voltage power supply   |

| SH/FC           | 5            | 5            | Shutdown and Switch frequency control |

| SS              | 6            | 6            | Soft startup control                  |

| GNDA            | 7            | 7            | Input side low voltage ground         |

| RSTb            | 8            | 8            | Reset fault condition                 |

| FLTb            | 9            | 9            | Fault condition signal                |

| RDY             | 10           | 10           | UVLO ready signal                     |

| IN+             | 11           | 11           | Driver control plus                   |

| IN–             | 12           | 12           | Driver control minus                  |

| VSSB            | 13, 15       | 13, 15       | Output side low voltage power supply  |

| VMID            | 16           | 16           | Drain reference for driven switch     |

| CLMP            | 17           | 17           | Miller clamp                          |

| VL              | 18           | 18           | Low gate drive                        |

| VH              | 19           | 19           | High gate drive                       |

| VDDB            | 20           | 20           | Output side low voltage power supply  |

| DSAT            | 21           | 21           | Desaturation detection input          |

| NC <sup>1</sup> | 14, 22       | 14, 22       | No connect                            |

| COMP            | 23           | 23           | dc/dc compensation                    |

| VSNS            | 24           | 24           | dc/dc voltage feedback                |

### Note:

1. No Connect. These pins are not internally connected. To maximize CMTI performance, these pins should be connected to the ground plane.

## 6. Packaging

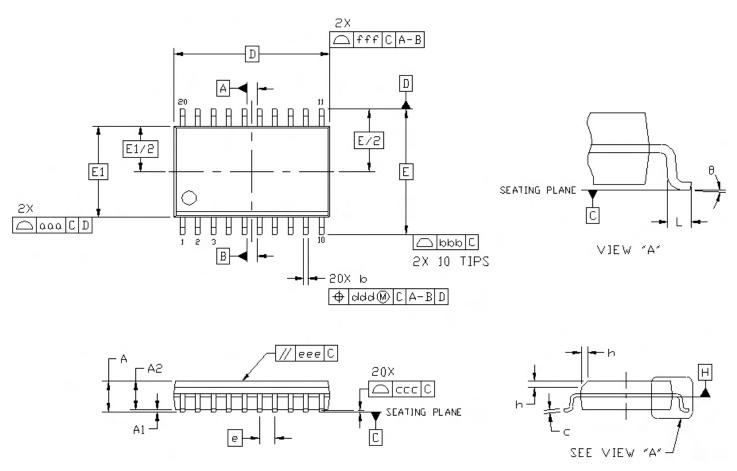

### 6.1 Package Outline: 20-Pin Wide Body SOIC

The figure below illustrates the package details for the Si8281/82 in a 20-Pin Wide Body SOIC. The table lists the values for the dimensions shown in the illustration.

Figure 6.1. 20-Pin Wide Body SOIC

| Symbol | Millimeters |      |  |

|--------|-------------|------|--|

|        | Min         | Мах  |  |

| A      | —           | 2.65 |  |

| A1     | 0.10        | 0.30 |  |

| A2     | 2.05        | _    |  |

| b      | 0.31        | 0.51 |  |

| С      | 0.20        | 0.33 |  |

| D      | 12.80 BSC   |      |  |

| E      | 10.30       | BSC  |  |

| E1     | 7.50 BSC    |      |  |

| e      | 1.27        | BSC  |  |

| L      | 0.40        | 1.27 |  |

| h      | 0.25        | 0.75 |  |

| θ      | 0°          | 8°   |  |

| Symbol | Millimeters |      |  |

|--------|-------------|------|--|

|        | Min         | Мах  |  |

| aaa    | —           | 0.10 |  |

| bbb    | _           | 0.33 |  |

| CCC    | _           | 0.10 |  |

| ddd    | _           | 0.25 |  |

| eee    | _           | 0.10 |  |

| fff    | _           | 0.20 |  |

### Note:

1. All dimensions shown are in millimeters (mm) unless otherwise noted.

2. Dimensioning and Tolerancing per ANSI Y14.5M-1994.

3. This drawing conforms to JEDEC Outline MS-013, Variation AC.

4. Recommended reflow profile per JEDEC J-STD-020C specification for small body, lead-free components.

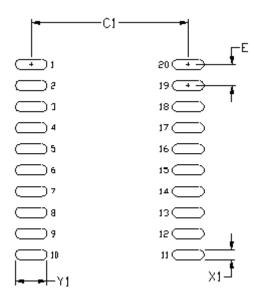

### 6.2 Land Pattern: 20-Pin Wide Body SOIC

The figure below illustrates the recommended land pattern details for the Si8281/2 in a 20-Pin Wide Body SOIC. The table lists the values for the dimensions shown in the illustration.

Figure 6.2. PCB Land Pattern: 20-Pin Wide Body SOIC

### Table 6.1. 20-Pin Wide Body SOIC Land Pattern Dimensions<sup>1, 2</sup>

| Dimension | Feature                                                                                                                                  | (mm) |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------|------|

| C1        | Pad Column Spacing                                                                                                                       | 9.40 |

| E         | Pad Row Pitch                                                                                                                            | 1.27 |

| X1        | Pad Width                                                                                                                                | 0.60 |

| Y1        | Pad Length                                                                                                                               | 1.90 |

|           | based on IPC-7351 design guidelines for Density Level B (Median L<br>at Maximum Material Condition (MMC), and a card fabrication tolerar | ,    |

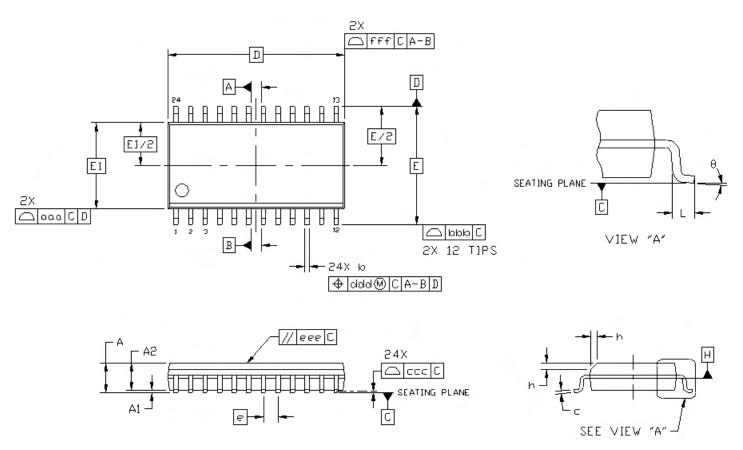

### 6.3 Package Outline: 24-Pin Wide Body SOIC

The figure below illustrates the package details for the Si8283/4 in a 24-Pin Wide Body SOIC. The table lists the values for the dimensions shown in the illustration.

Figure 6.3. 24-Pin Wide Body SOIC

| Symbol | Millimeters |      |  |

|--------|-------------|------|--|

|        | Min         | Мах  |  |

| A      | -           | 2.65 |  |

| A1     | 0.10        | 0.30 |  |

| A2     | 2.05        | _    |  |

| b      | 0.31        | 0.51 |  |

| С      | 0.20        | 0.33 |  |

| D      | 15.40       | BSC  |  |

| E      | 10.30 BSC   |      |  |

| E1     | 7.50        | BSC  |  |

| e      | 1.27        | BSC  |  |

| L      | 0.40        | 1.27 |  |

| h      | 0.25        | 0.75 |  |

| θ      | 0°          | 8°   |  |

| ааа    | _           | 0.10 |  |

| bbb    | -           | 0.33 |  |

| Symbol | Millimeters |      |  |

|--------|-------------|------|--|

|        | Min         | Мах  |  |

| 200    | _           | 0.10 |  |

| ddd    | _           | 0.25 |  |

| eee    | _           | 0.10 |  |

| fff    | _           | 0.20 |  |

| Nata   |             |      |  |

### Note:

1. All dimensions shown are in millimeters (mm) unless otherwise noted.

2. Dimensioning and Tolerancing per ANSI Y14.5M-1994.

3. This drawing conforms to JEDEC Outline MS-013, Variation AD.

4. Recommended reflow profile per JEDEC J-STD-020 specification for small body, lead-free components.

### 6.4 Land Pattern: 24-Pin Wide Body SOIC

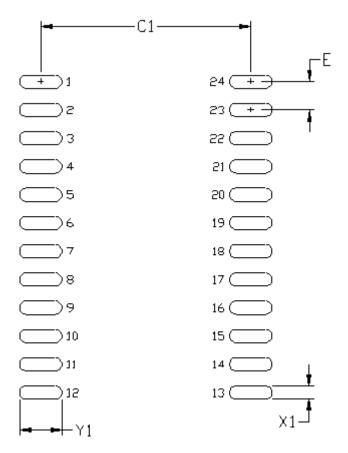

The figure below illustrates the recommended land pattern details for the Si8283/4 in a 24-Pin Wide Body SOIC. The table lists the values for the dimensions shown in the illustration.

Figure 6.4. PCB Land Pattern: 24-Pin Wide Body SOIC

### Table 6.2. 24-Pin Wide Body SOIC Land Pattern Dimensions<sup>1, 2</sup>

| Dimension | Feature            | (mm) |

|-----------|--------------------|------|

| C1        | Pad Column Spacing | 9.40 |

| E         | Pad Row Pitch      | 1.27 |

| X1        | Pad Width          | 0.60 |

| Y1        | Pad Length         | 1.90 |

| Neter     |                    |      |

#### Note:

1. This Land Pattern Design is based on IPC-7351 design guidelines for Density Level B (Median Land Protrusion).

2. All feature sizes shown are at Maximum Material Condition (MMC), and a card fabrication tolerance of 0.05 mm is assumed.

### 6.5 Top Marking: 20-Pin and 24-Pin Wide Body SOIC

Si8281/82 Top Marking

Si8283/84 Top Marking

### Table 6.3. Si8281/2/3/4 Top Marking Explanation

| Line 1 Marking: | Customer Part Number      | Si8281, Si8282, Si8283, Si8284 = ISOdriver                  |

|-----------------|---------------------------|-------------------------------------------------------------|

|                 |                           | U = UVLO level: B = 9 V; C = 12 V                           |

|                 |                           | V = Isolation rating: D = 5.0 kV                            |

| Line 2 Marking: | RTTTTT = Mfg Code         | Manufacturing code from the Assembly Purchase Order form    |

|                 |                           | "R" indicates revision                                      |

| Line 3 Marking: | Circle = 43 mils Diameter | "e4" = Pb-Free Symbol                                       |

|                 | Left-justified            |                                                             |

|                 | YY = Year                 | Assigned by the assembly house. Corresponds to the year and |

|                 | WW = Workweek             | workweek of the mold date.                                  |

# **Table of Contents**

| 1. | Ordering Guide                                                                                                        | . '             | 1 |

|----|-----------------------------------------------------------------------------------------------------------------------|-----------------|---|

| 2. | System Overview                                                                                                       | . 2             | 2 |

|    | 2.1 Isolation Channel Description                                                                                     | . 2             | 2 |

|    | 2.2 Device Behavior                                                                                                   | . 2             | 2 |

|    | 2.3 Input                                                                                                             | . :             | 3 |

|    | 2.4 Driver Side Output                                                                                                |                 | 3 |

|    | 2.5 Fault (FLTb) Pin                                                                                                  |                 | 3 |

|    | 2.6 Reset (RSTb) Pin                                                                                                  |                 | 3 |

|    | 2.7 Ready (RDY) Pin                                                                                                   |                 | 3 |

|    | 2.8 Undervoltage Lockout (UVLO)                                                                                       | . :             | 3 |

|    | 2.9 Desaturation Detection                                                                                            | . 4             | 4 |

|    | 2.10 Soft Shutdown                                                                                                    | . 4             | 4 |

|    | 2.11 Miller Clamp                                                                                                     | . !             | 5 |

|    | 2.12 DC-DC Converter Application Information                                                                          |                 |   |

|    | 2.12.1 External Transformer Driver                                                                                    |                 |   |

|    | 2.12.2 Output Voltage Control                                                                                         |                 |   |

|    | 2.12.4 Thermal Protection                                                                                             |                 |   |

|    | 2.12.5 Cycle Skipping                                                                                                 |                 |   |

|    | 2.12.6 Shutdown (Si8283 and Si8284 Only)                                                                              |                 |   |

|    | 2.12.7       Soft Start (Si8283 and Si8284 Only)         2.12.8       Programmable Frequency (Si8283 and Si8284 Only) |                 |   |

|    | 2.12.9 Low Supply Voltage Configuration                                                                               |                 |   |

|    | 2.12.10 High Supply Voltage Configuration                                                                             | . 8             | 8 |

|    | 2.13 Transformer Design                                                                                               | .1(             | 0 |

| 3. | Applications Information                                                                                              | 1               | 1 |

|    | 3.1 Recommended Application Circuits.                                                                                 | .1 <sup>.</sup> | 1 |

|    | 3.1.1 Inputs                                                                                                          |                 |   |

|    | 3.1.2 Reset, RDY, and Fault                                                                                           |                 |   |

|    | 3.1.3 Desaturation.       3.1.4 Driver Outputs                                                                        |                 |   |

|    | 3.2 Layout Considerations                                                                                             |                 |   |